High density European Rad-Hard SRAM-based FPGA: Abound-Logic-based first validated prototypes (next generation FPGA)

Programme Reference

T701-301ED

Status

Closed

Country

France

Start Date

2013

End Date

2019

Programme: TDE Prime Contractor: NANOXPLORE

Subcontractors:

MICROCHIP TECHNOLOGY NANTES • France

STMICROELECTRONICS SA • France

Teledyne e2v Semiconductors SAS • France

Objectives

The objective is to develop the first high capacity European Radiation Hardened By Design (RHBD) reprogrammable Field Programmable Gate Array (FPGA) using a newly validated innovative FPGA architecture from Abound Logic, France. It aims to ultimately complement the European offering and challenge the current US supply (in order to be after 2014/2015 in a position to 1) replace US origin parts from Actel RTAX4000 and beyond, as well as the Rad-tolerant Xilinx Virtex 4 rad-tolerant series; 2) and to be competitive with the soon-to-appear Rad-Hard Virtex-5 series).

Description

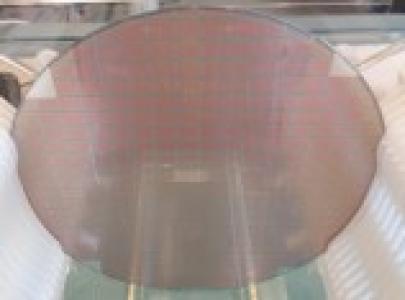

New satellite designs entail more and more complex functionalities implemented in Field Programmable Gate Arrays (FPGA). Although Europe is far behind the US in the availability of powerful FPGAs, the first European reprogrammable radiation hard FPGAs offer the unique opportunity to develop new, larger capacity European ITAR-free FPGAs including the silicon parts, software hardware development and programming tools to be able to cover the big gap. The new Abound Logic FPGA innovative architecture provides a mix of programmable logic, and math and memory hard blocks that enable the applications requirements. This new FPGA will offer roughly 2.5M ASIC equivalent gates and will advantageously compete with its US competitors and to overcome the existing FPGA technology gap.The activity includes first an assessment on the application of rad-hard techniques to the current Abound Logic commercial Raptor FPGA followed by the development program according to the standard ECSS-Q-ST-60-02C that will enable to move to a rad-hard version of the Raptor design. It will be starting from the specification, functional and verification test plan, passing through the architectural and detail design phases; getting the final layout and finishing with the first samples (prototypes) including the functional validation. The rad-hard by design FPGA prototype will be based on an advanced deep sub micron Complementary Metal-Oxide-Semiconductor (CMOS) process, the ST Microelectronics 65nm CMOS process developed under ESA TRP funding.This activity will be complementing the FP7 granted proposal RAdiation Hardening by Design a Highly Integrated FPGA for Space (RAHSHIFFS), which includes a consortium of users that will be using the first prototypes and will be performing the radiation testing of the prototypes.This activity is included in the overall Atmel plan to introduce a series, beyond the one considered in the present activity, of Abound Logic based RHBD FPGAs using STM 65nm CMOS technology, which might lead to 3 different chip sizes and in a variety of packages.

• Application domain: Generic Technologies

•

Technology Domain:

1 - On-board Data Subsystems

1 - On-board Data Subsystems

•

Competence Domain:

1-EEE Components, Photonics, MEMS

1-EEE Components, Photonics, MEMS

• Initial TRL: TRL 2

• Target TRL: TRL 4

• Achieved TRL: TRL 5

•HarmoRoadMap: N/A

•IPC Document: ESA/IPC(2010)3,ADD.4||ESA/IPC(2013)3

•Public Document: