# VHDR

#### Very High Data Rate Breadboard Receiver for Earth to Lunar Comms

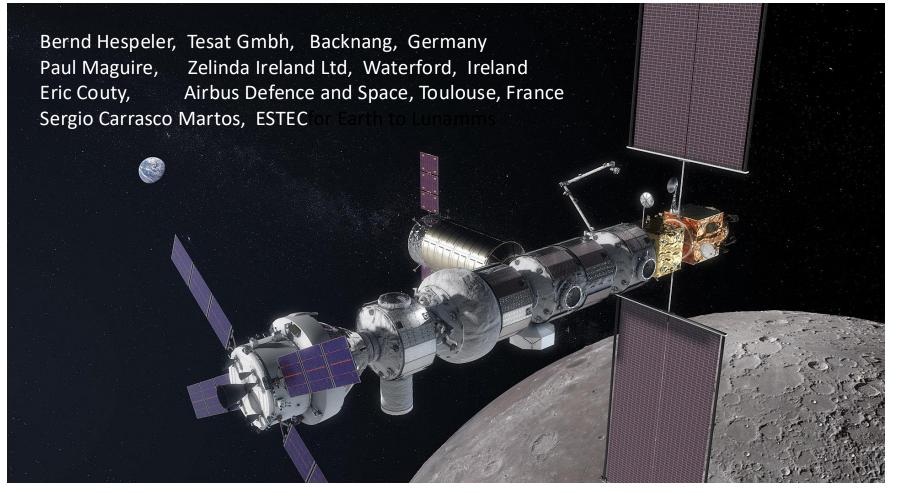

# VHDR – Cislunar Space Exploration plan Overview

#### Lunar Orbital Platform – Gateway (LOP-G)

The next step in Human Space Exploration is a space station in lunar orbit intended to serve as

- a communication hub, between Earth, Moon (inc lander, rovers, visiting vehicles) and lunar relay satellites.

- science laboratory,

- short-term habitation module for astronauts,

- transfer station to the exploration of the Moon and Mars

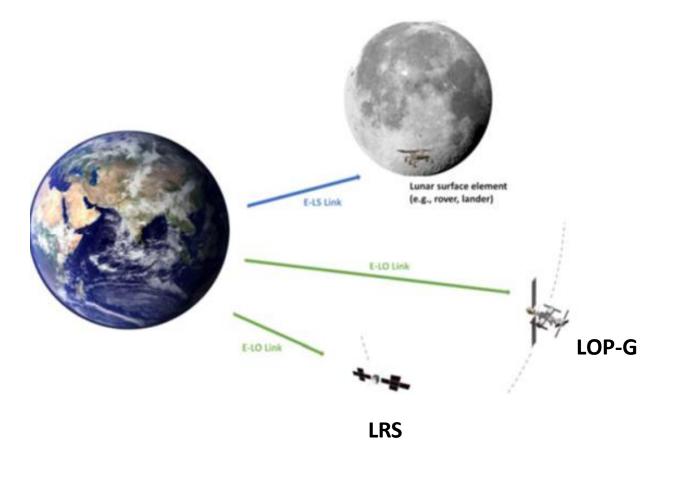

Additionally a constellation of Lunar Relay Satellites (LRS) probably in frozen Elliptical inclined lunar orbit (stable for > 10 years without station keeping).

Generic Lunar surface elements communicating both direct with earth or with LOP-G or LRS.

# VHDR – Comms Links

- All three links require receivers for comms from earth (E->LO and E->LS forward links)

- Potential comms links Orbiters to lunar surface also needs receiver (LO->LS link).

# VHDR – Uplink Comms Requirements

ITU and SFCG recommend **K-band** for high rate Space Research comms in Lunar region, specifically 22.55 – 23.50 GHz.

- Bandwidth limited to ~110 MHz

- For bandwidth efficiency SRRC OQPSK modulation (better than GMSK)

- AR4JA LDPC coding (as specified for TM downlink)

- 4 code rates/length combinations (1/2 16k, 2/3 16k, 4/5 16k, ½ 1K)

- Information rates up to 160 Mbps (4/5 code) with 100 Msym/S

To keep operations simple Handover from different ground station should be:

- Autonomous acquisition

- Autonomous data rate detection (from 4 preselected in range 10 -> 100 Msyms/s)

- Autonomous code rate detection

- Autonomous block length detection

- Fade mitigation

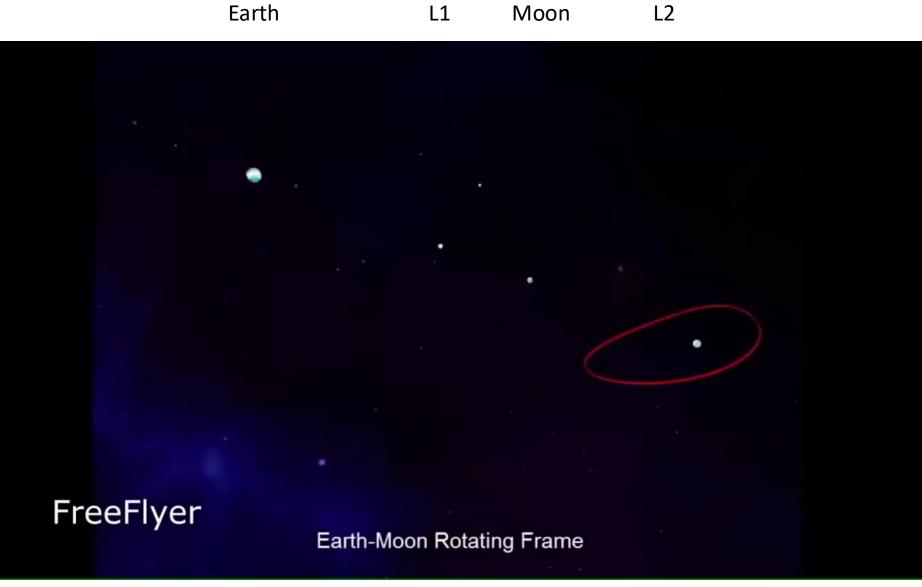

#### VHDR – LOP-G orbit Near Rectilinear Halo Orbit (NRHO) Animation

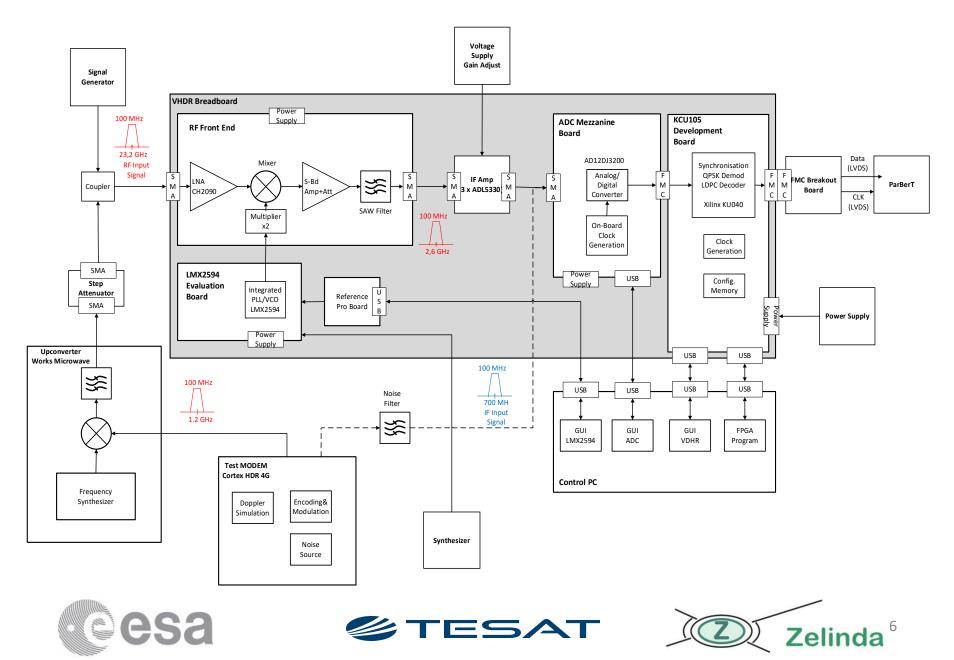

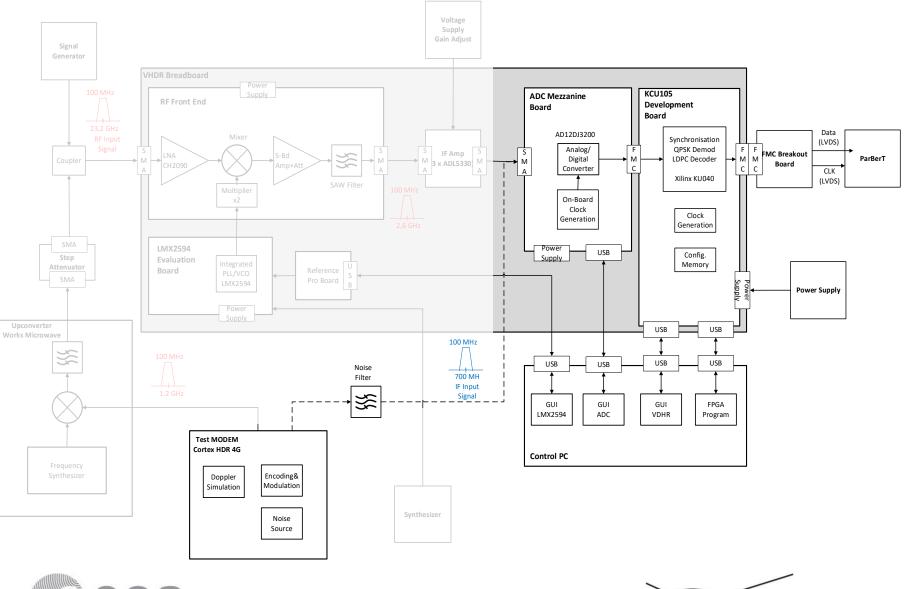

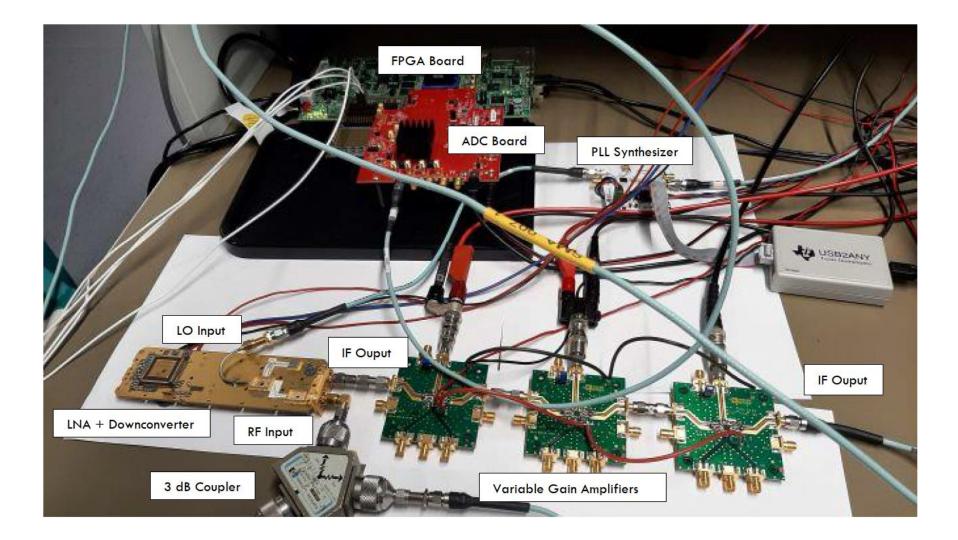

### **Breadboard Overview**

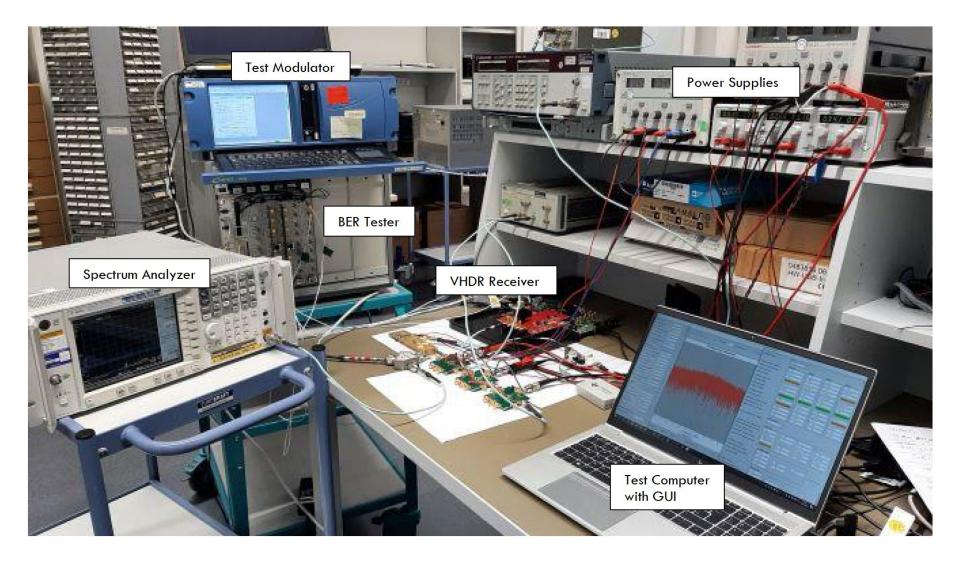

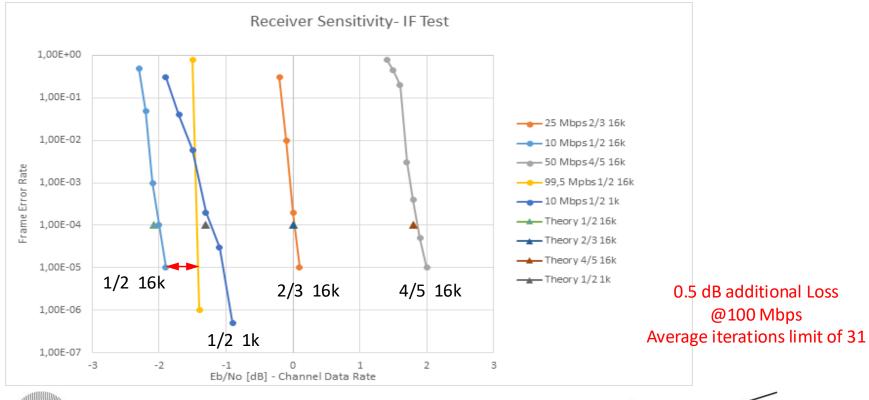

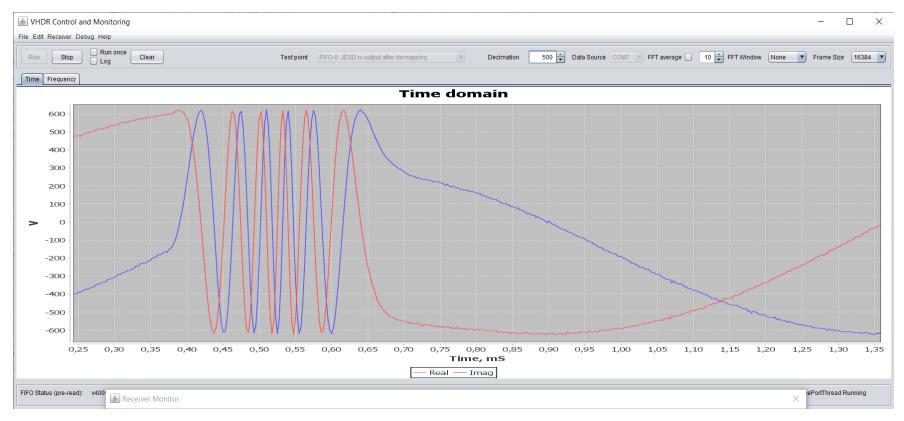

## Breadboard - IF Test @ 2.5 GHz

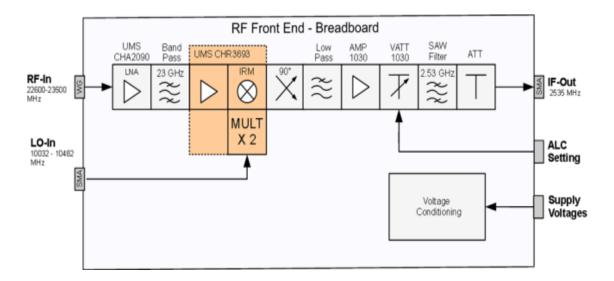

# RF front end (Tesat)

- The CHA2090 LNA is a three-stage self-biased wide band monolithic low noise amplifier .

- 23 GHz Bandpasss filter of TESAT design realized as microstrip MIC filter.

- CHR3693 is a multifunction chip which integrates: a balanced cold FET mixer; a times two LO multiplier; a RF self-biased LNA.

- ~3 GHz lowpass IF filter is a TESAT design again realized as microstrip MIC filer.

- IF amplifier and attenuator MMICs are standard TESAT designs manufactured at UMS on a space qualified GaAs process.

### **Breadboard Hardware**

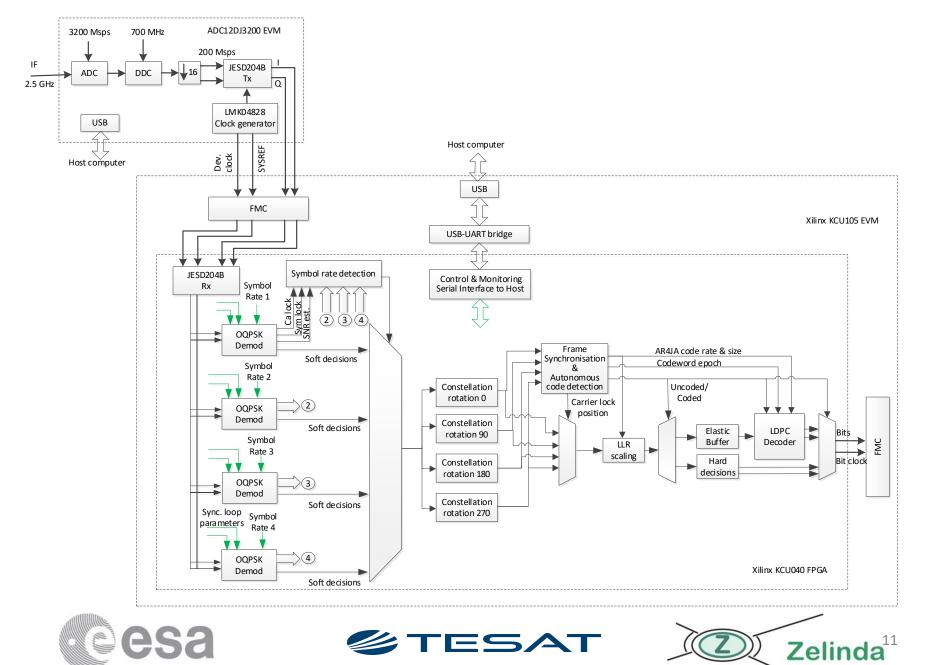

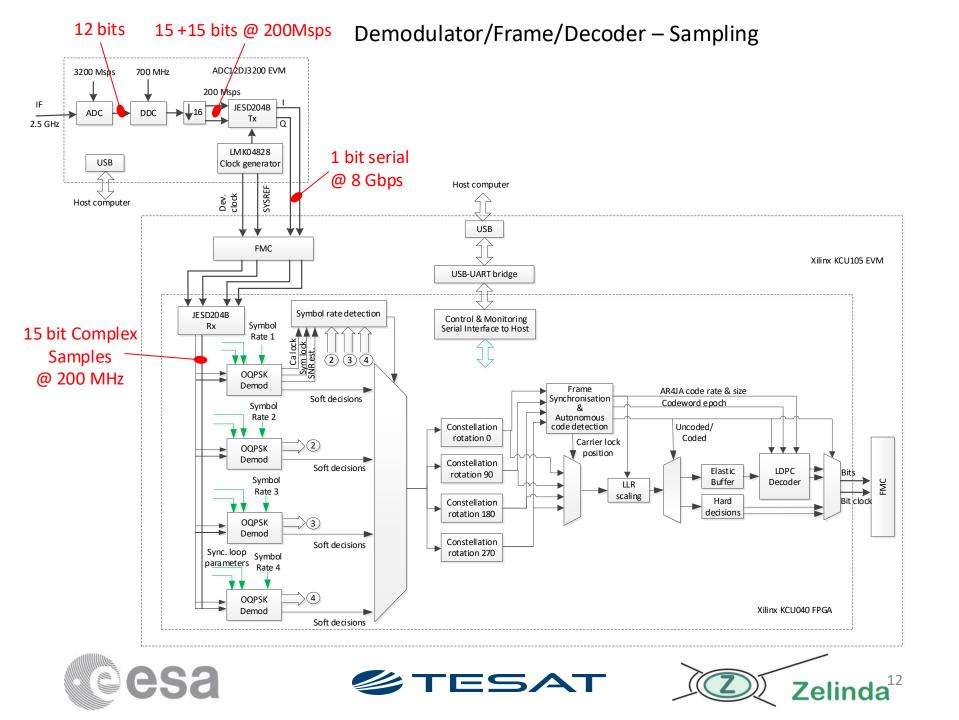

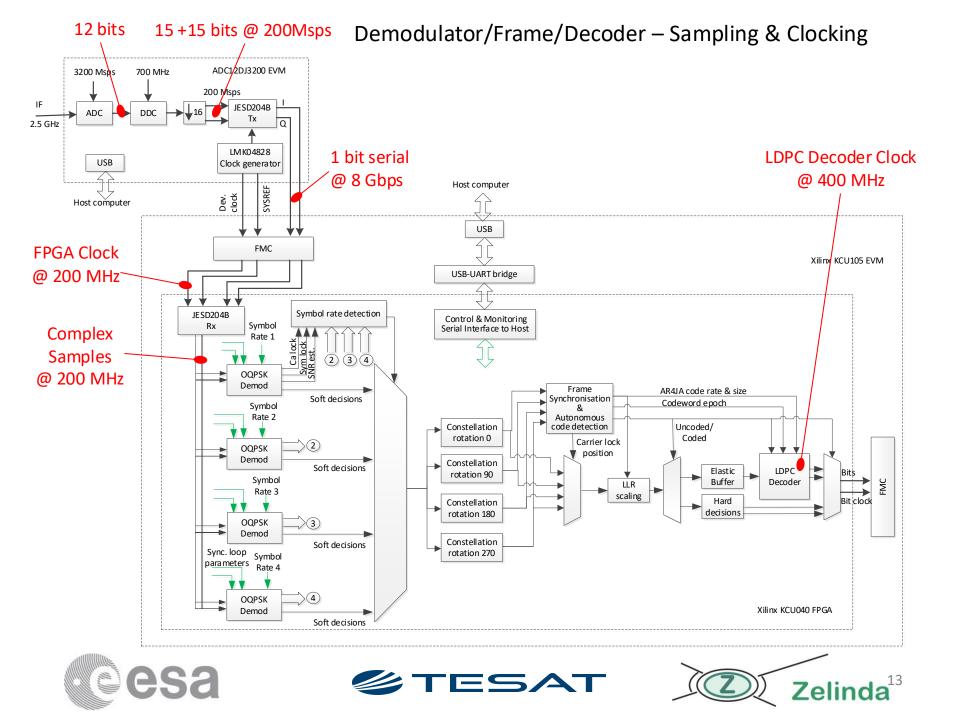

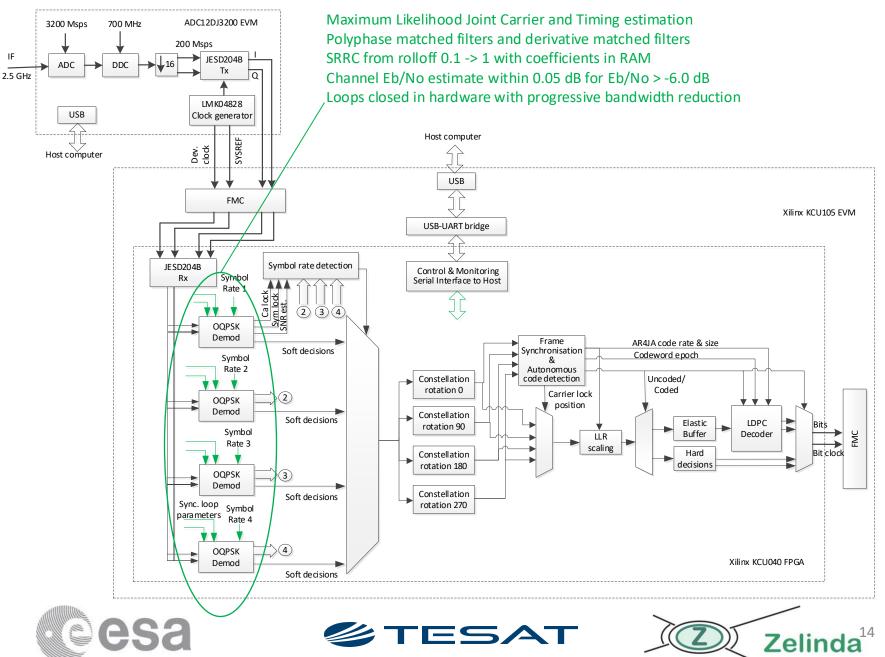

# Demodulator / Decoder Requirements

- Modulation: SRRC-OQPSK with symbol rates between 10-100 Msym/s (bandwidth limited)

- Channel coding: CCSDS AR4JA **LDPC codes** {1/2, 2/3, 4/5}, 16k, and ½, 1k

- Autonomous detection of channel symbol rate from a preconfigured list of 4 symbol rates

- Autonomous detection of LDPC code rate and block length

- Fade mitigation ("Free Wheel" through fades)

- Target Frame Error Rate (FER) of 1E-4

- Doppler shift of up to +/-150 kHz and Doppler rate of up to +/-120 Hz/s

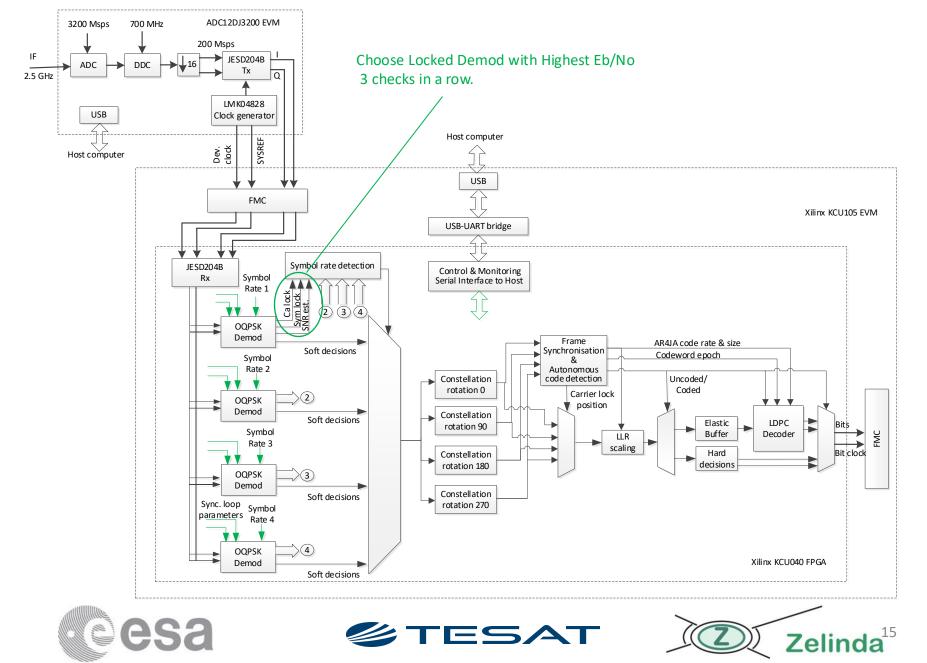

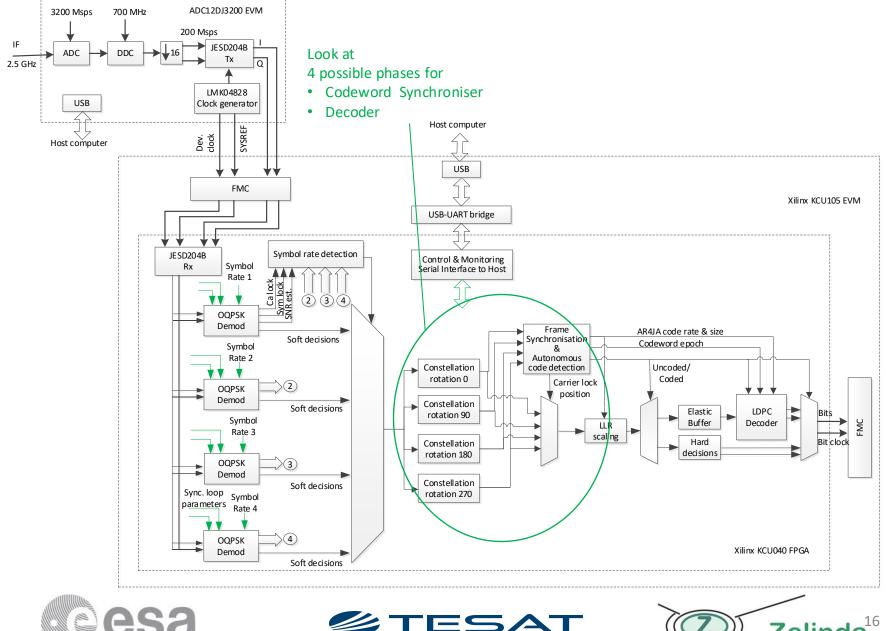

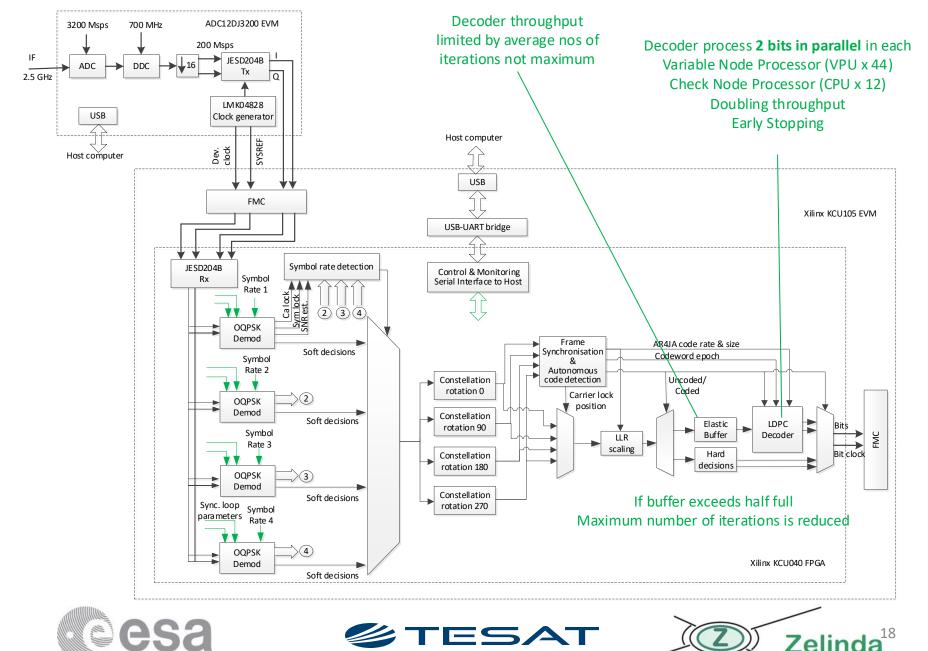

#### DSP: Demodulator / Codeword Sync / Decoder Overview

#### Demodulators

#### Demodulator - Autonomous Symbol rate detection

#### Codeword Sync – Autonomous Code Rate & Length

Zelin

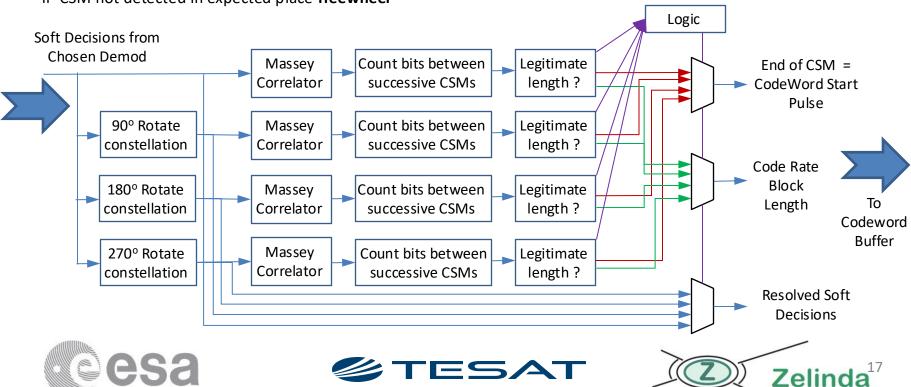

#### Codeword Sync – Autonomous Code Rate & Length Algorithm

|                     | Block Size | 1,024 | 4,096 | 16,384 |

|---------------------|------------|-------|-------|--------|

| Unique              | Rate 4/5   | 1,280 | 5,120 | 20,480 |

| Codeword<br>Lengths | Rate 2/3   | 1,536 | 6,144 | 24,576 |

|                     | Rate 1/2   | 2,048 | 8,192 | 32,768 |

- Maintain 4 counters counting bits between detected Code Sync Markers (CSMs ) from Massey Correlators

- Codeword lengths are unique, confusion possible only if 2 consecutive CodeWord Sync Markers missed (3\*2048=4\*1536)

- If (count between detections == codeword length or twice codeword length) then declare found

If CSM not detected in expected place freewheel

#### LDPC Decoder

# Freewheeling through Fades

As depth of fade increases :

- FER approaches 1 (~0.5 dB Fade) "immediate" recovery < 1 codeword

- Carrier phase flips => bit slips (a few dB) => Loss of Codeword synchronisation quick recovery, < 2 codewords

- Loss of carrier lock and loss of Bit sync lock quick recovery < 1 mS

- Loss of carrier frequency estimate & bit clock complete re-acquisition required

#### Mitigation

- Codeword Sync "freewheel" will generate pulses at appropriate intervals for upto 4095 missed Codewords

- Leave Carrier and Bit Sync loops in narrow band tracking mode to stay on frequency (until time out)

## Testing

- Test FPGA stand alone (Demodulators, Sync detection, Code Rate & Lenth detection, LDPC Decoder)

- Signal from wavwform sample look up (exact Eb/No setting)

- BER from LDPC "for free"

- FER from LDPC "for free"

- Acquisition time from in built timers

- Test FPGA and ADC with IF input

- Analogue signal generator,

- BER Tester (measures errors in undecoded codewords)

- Test at RF

- Analogue Signal generator and upconvertor, BER Tester

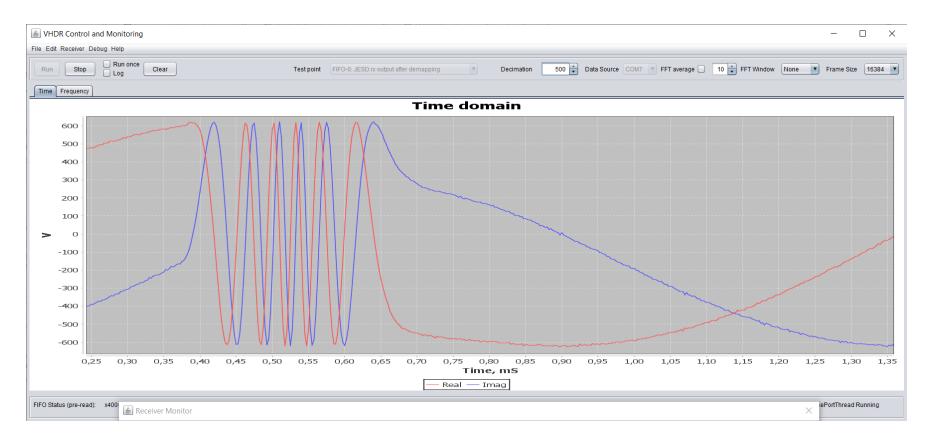

### Testing – FPGA Standalone

98 Msyms/S, <sup>1</sup>/<sub>2</sub> rate 16384 info block, channel Ecs/No = -1.75, Eb/No = +1.25 dB

| VHDR Control and Monitoring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                           |                                          | - 0 ×                                               |                                         |                                       |                              |              |                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------|-----------------------------------------------------|-----------------------------------------|---------------------------------------|------------------------------|--------------|----------------|

| In Edit Signal Receiver Debug Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |                                          |                                                     | , III III III III III III III III III I |                                       |                              |              |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                           |                                          |                                                     |                                         |                                       | alculator (2)                |              |                |

| Run Stop Log Clear 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | rest point None Decimation 1 😴 Data Sou   | urce COM5 T FFT average 10 FFT Window No | e Frame Size 0                                      |                                         |                                       |                              |              |                |

| Time Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                           |                                          |                                                     |                                         |                                       |                              |              |                |

| Time domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                           |                                          |                                                     |                                         | Receiver Monitor                      |                              |              | ×              |

| 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                           |                                          | Demodulator 3                                       | ×                                       |                                       | ALC                          |              |                |

| 0.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Configure Receiver                        |                                          | Carrier Recovery                                    |                                         | Input Power (dBFs)                    | -25.03                       |              |                |

| 0.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Symbol Rate Detection                     | ^                                        | Carrier Rest Frequency                              | 0.0 Hz                                  |                                       |                              |              |                |

| 0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Manual Demod Selection                    |                                          | PLL Log2 Proportional Constant                      | 11                                      | Configured Carrier Frequency (        | Demod 0 Demod 1              | 0.0          | Demod 3        |

| 0.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                           |                                          | PLL Log2 Integral Constant                          | 16                                      | Apparent Frequency offset (Hz)        | -115.6 -976.6                | 1.544.2      | 5.973.1        |

| > 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Demod to Use 0                            |                                          | PLL Integrator Leak                                 | 3                                       | Carrier Lock Quality                  | -6 -11                       | -12          | 83             |

| Signal Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Frame Synchroniser                        |                                          | PLL Integrator Monitor TC                           | 0                                       | Carrier Lock Status                   |                              |              |                |

| Signal Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Indefinite freewheel                      |                                          | PLL Integrator Limit                                | 150.000.0 Hz                            |                                       | Unlocked Unlocked            | Unlocked     | Locked, Narrow |

| Signal Source Stored Wav                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Frames to FreeWheel 13                    |                                          | PLL log2 Bandwidth reduction                        | 3                                       | Configured Symbol Rate                | 9.800.000.0 18.798.828.1     | 31,347,656.3 | 98.000,000.0   |

| Stored waveform Type Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Coded CSM Detect Threshold -140           |                                          | PLL Lock Threshold                                  | 60                                      | Symbol Rate Offset                    | 79.4 -65.8                   | 890.1        | 119.0          |

| Waveform Decimation ratio 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Uncoded CSM Detect Threshold -18          |                                          | PLL Unlock Threshold                                | 0                                       | Timing Lock Quality                   | -284 -275                    | -276         | 21             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                           | 0.80 0.85 0.                             | Acq PLL Loop Bandwidth (2BI)                        | 490.885.8 Hz                            | Timing Lock Status                    | Unlocked Unlocked            | Unlocked     | Locked, Narrow |

| Noise Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CodeWord FIFO Buffer                      |                                          | PLL Damping Factor                                  | 1.59                                    | I/Q Stagger (symbols)                 | 0.500 0.500                  | 0.500        | 0.500          |

| Enable AWGN addition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                           |                                          |                                                     |                                         | Co-Timing Loop Lock                   | Unlocked Unlocked            | Unlocked     | Locked         |

| Signal gain (dB) -13.00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | rei Reset FIFO Reset FIFO                 | 10 Baud; Parity Odd                      | Sta Symbol Timing<br>Symbol Rest Frequency          | 98.000.000.0 Hz                         | Mean Symbol Absolute Amplitude        | 16.10 11.64                  | 17.89        | 21.17          |

| Noise gain (dB) -1.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | LDPC Decoder                              |                                          | PLL Log2 Proportional Constant                      | 9                                       | Apparent Eb/No I Chan (dB)            | < -4.00                      | < -4.00      | -1.75          |

| Monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Early Stopping                            |                                          | PLL Log2 Integral Constant                          | 11                                      | Apparent Eb/No Q Chan (dB)            | < -4.00                      | < -4.00      | -1.77          |

| Monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Demod 0 Demod 1 Demod 2                   | Demod 3                                  | PLL Integrator Leak                                 | 3                                       |                                       |                              |              |                |

| Measured Signal Power (dBFS) -29.02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Maximum Iterations < 1/2 full             |                                          | PLL Integrator Monitor TC                           | 0                                       | Chosen Demod (green = detected)       | Demod Selector               |              |                |

| Measured Noise Power (dBFS) -27.24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Maximum Iterations > 1/2 full 300 230 220 | 28                                       | PLL Integrator Limit                                | 5,000.0 Hz                              |                                       |                              |              |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 300 230 220                               |                                          | PLL log2 Bandwidth reduction                        | 3                                       |                                       | Frame Sync                   |              |                |

| CINo (dB) 81.23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Data Output delay                         |                                          | PLL Lock Threshold                                  | 10                                      | Framing Found, Massey Metric, Eb/No   | Yes -127                     |              | dB             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Gate delay 0                              |                                          | PLL Unlock Threshold                                | -50                                     | Phase, Phase/Code Flips, Old Phases   | 90 2                         | 180          | 90             |

| Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                           | Write                                    |                                                     |                                         | Frame Type, Old Frame Types           | 16.384, r = 1/2              | 16k, r= 1/2  | 16k, r= 1/2    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                           |                                          | Acq PLL Loop Bandwidth (2BI)                        | 48.568.9 Hz                             | Coded CSMs FoundMissed/Unexp          | 41.217.417 625.435           |              | at 14,979      |

| About VHDR Probe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ×                                         |                                          | PLL Damping Factor                                  | 1.41                                    | Uncoded CSMs Found/Missed/Unexp       | 0 0                          | 299,967      | at 7.325       |

| VHDR Java GUI Revision: 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                           |                                          | Co-Timing                                           | ]                                       |                                       | CodeWord buffer              |              | -              |

| 03 May 2022                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                           |                                          |                                                     | V                                       | Gap between Codewords                 | 64                           |              |                |

| (c) Zelinda Ireland Ltd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                           |                                          | log2 Loop Gain                                      | 1                                       | Wrong Gap Count, Gap, Old Gap         | 0                            |              | Reset Counts   |

| Intended for VHDL Repository version 75 on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                           |                                          | Phase Error Limit                                   | 0.100                                   | Frames Received / Frame Resyncs       | 41.842.848 0                 |              |                |

| Address Map Numbers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                           |                                          | log2 Bandwidth reduction                            | 1                                       | Code Words in Buffer                  | 0.86                         |              |                |

| VHDL Register Address Map Version number 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                           |                                          | Lock Threshold                                      | 0.010 Sym                               |                                       | LDPC Decoder                 |              |                |

| XML Register Address Map Version number 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                           |                                          | Unlock Threshold                                    | 0.015 Sym                               | Absolute LLR Amp                      | 10                           |              | ]              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                           |                                          | Time Constant                                       | 167.772 mS                              | Decoder Iterations / Bits corrected   | 35 4,147                     |              | Reset Counts   |

| XML Loaded Register Data Title Config 1 of D9 V and V procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                           |                                          |                                                     |                                         | Decoded Channel Bits / Errors         | 1.368.815.534.08 169.626.173 | 600          |                |

| Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                           |                                          | Demodulator Output Scaling Matched Filter Downshift |                                         | Apparent Channel BER                  | 0.123922                     |              | Reset BER      |

| VHDL Repository Revision Number 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |                                          | Matched Filter Downshift                            | 2                                       | Codewords Total / Successful / Failed | 41.842.843 41.772.935        | 69,907       |                |

| Stored Sample Information Rate 9.80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0 Mbps (undecimated)                      |                                          |                                                     | Write                                   | FER                                   | 0.00167070                   |              | Reset All      |

| Stored Sample Code Rate, k 1/2, 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                           |                                          |                                                     |                                         |                                       |                              |              | J              |

| Stored Sample Eb/No No No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |                                          |                                                     |                                         |                                       |                              |              |                |

| None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                           |                                          |                                                     |                                         |                                       |                              |              |                |

| A second s |                                           |                                          |                                                     |                                         |                                       |                              |              |                |

### Testing – FPGA Standalone

Demod #3 locked

#### 98 Msyms/S, 1/2 rate 16384 info block, channel Ecs/No = -1.75, Eb/No = +1.25 dB

| JUDR Control and Monitoring                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               | - 🗆 ×                                  |                 |                                       |                                  |                          |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------|-----------------|---------------------------------------|----------------------------------|--------------------------|

|                                                            | W VRR Control and Monitoring     -     -     X       File Edit Signal Receiver Debug Help     -     -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                               |                                        |                 |                                       |                                  |                          |

| Run Stop Run once Clear Test point                         | None Decimation 1 Data Source COM5 * FF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | FT average 10 FFT Window None | Frame Size 0                           |                 |                                       |                                  |                          |

| Time Frequency                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               |                                        |                 |                                       |                                  |                          |

|                                                            | Time domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                               |                                        |                 | Receiver Monitor                      |                                  |                          |

| 1.0                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               | Demodulator 3                          | ×               |                                       |                                  | \                        |

| 0.9                                                        | provide and the second s |                               | Carrier Recovery                       |                 | Input Power (dBFs)                    | ALC -25.03                       |                          |

| 0.8                                                        | Configure Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ×                             | Carrier Rest Frequency                 | 0.0 Hz          |                                       | -25.03                           |                          |

| 0.7                                                        | Symbol Rate Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                               | PLL Log2 Proportional Constant         | 11              |                                       | Demod 0 Demod 1                  | Demod 2 Demod 3          |

| 0.6                                                        | Manual Demod Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                               | PLL Log2 Integral Constant             | 16              | Configured Carrier Frequency (        | 0.0 0.0                          | 0.0                      |

| > 0.5                                                      | Demod to Use 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                               | PLL Integrator Leak                    | 3               | Apparent Frequency offset (Hz)        | -115.6 -976.6                    | 1.544.2 5.973.1          |

| ▲ Signal Source ×                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               | PLL Integrator Monitor TC              | 0               | Carrier Lock Quality                  | -6 -11                           | -12 83                   |

| Signal Type                                                | Frame Synchroniser                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                               | PLL Integrator Limit                   | 150.000.0 Hz    | Carrier Lock Status                   | Unlocked Unlocked                | Uni cked Locked. Narrow  |

| Signal Source Stored Wav                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               | PLL log2 Bandwidth reduction           | 3               | Configured Symbol Rate                | 9.800.000.0 18.798.828.1         | 31 47.656.3 98.000,000.0 |

| Stored waveform Type Signal                                | Frames to FreeWheel 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                               | PLL Lock Threshold                     | 60              | Symbol Rate Offset                    | 79.4 -65.8                       | 190.1 119.0              |

| Waveform Decimation ratio                                  | Coded CSM Detect Threshold -140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               | PLL Unlock Threshold                   | 0               | Timing Lock Quality                   | -284 -275                        | 276 21                   |

|                                                            | 2 Uncoded CSM Detect Threshold -18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0.80 0.85 0.90                | Acg PLL Loop Bandwidth (2BI)           | 490.885.8 Hz    | Timing Lock Status                    | Unlocked Unlocked                | Locked Locked, Narrow    |

| Noise Configuration                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               | PLL Damping Factor                     | 1.59            | I/Q Stagger (symbols)                 | 0.500                            | 0.500                    |

| Enable AWGN addition                                       | CodeWord FIFO Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                               |                                        |                 | Co-Timing Loop Lock                   | Unlocked Unlocked                | Un pcked                 |

| Signal gain (dB) -13.00                                    | Reset FIFO Reset FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0 Baud; Parity Odd Sta        | Symbol Timing<br>Symbol Rest Frequency | 98.000.000.0 Hz | Mean Symbol Absolute Amplitude        | 16.10 11.64                      | 17.9 21.17               |

| Noise gain (dB) -1.90                                      | LDPC Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                               | PLL Log2 Proportional Constant         | 9               | Apparent Eb/No I Chan (dB)            | < -4.00                          | < -4.0                   |

|                                                            | Early Stopping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                               | PLL Log2 Integral Constant             | 11              | Apparent Eb/No Q Chan (dB)            | < -4.00                          | < -4.00                  |

| Monitor                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               | PLL Integrator Leak                    | 3               |                                       |                                  |                          |

| Measured Signal Power (dBFS) -29.02                        | Demod 0         Demod 1         Demod 2         Demod 3           Maximum Iterations < 1/2 full         450         400         400         90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                               | PLL Integrator Monitor TC              | 0               | Chosen Demod (green = detected)       | Demod Selector                   |                          |

| Measured Noise Power (dBFS) -27.24                         | 400 000 000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                               | PLL Integrator Limit                   | 5,000.0 Hz      | Cilosen Deniod (green = delected)     |                                  |                          |

|                                                            | Maximum Iterations > 1/2 full 300 230 220 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                               | PLL log2 Bandwidth reduction           | 3               |                                       | Frame Sync                       |                          |

| C/No (dB) 81.23                                            | Data Output delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                               | PLL Lock Threshold                     | 10              | Framing Found, Massey Metric, Eb/No   | Yes -127                         | 1.25 dB                  |

|                                                            | Gate delay 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                               | PLL Unlock Threshold                   | -50             | Phase, Phase/Code Flips, Old Phases   | 90 2                             | 180 90                   |