Prototyping and Characterisation of Radiation Hardened SiC MOS Structures.

Programme Reference

T723-409QT

Status

Closed

Country

Spain

Start Date

2015

End Date

2019

Programme: TDE Prime Contractor: ALTER TECHNOLOGY TUV NORD S.A.

Subcontractors:

D+T MICROELECTRONICA, A.I.E. • Spain

UNIV VALENCIA • Spain

Objectives

The aim of the activity will be to perform the prototyping and characterisation of radiation hardened (SEE TID) SiC gate oxide materials through use of an elementary MOS capacitor structure for the optimisation of the gate oxide process parameters. The output of this activity shall help to identify the MOS structure required for the development, evaluation and qualification of radiation hardened high-voltage SiC power-MOSFETs in future activities.

Description

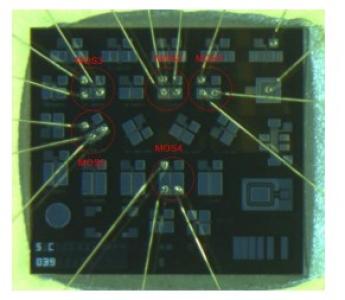

The study will be focused on the prototyping of SiC MOS capacitor structures with the main goal to characterise the overall quality and stability of the gate oxide to SiC interface to gate stress as well as the radiation performances of SiC gate oxide in terms of SEE and TID testing. This study will be preparatory and supporting the planned developments of discrete radiation-hardened SiC power-MOSFETs for use in the space environment and space applications.The main features of SiC base material are known (high energy gap, high electric field breakdown in combination with reasonably high electron mobility and high thermal conductivity) leading to the following expected and in some cases already proven capabilities for power applications, namely: low on-state voltage, low recovery charge, fast turn-on and turn-off, high blocking voltage, higher reliable operating junction temperature high power density.On the other hand, the stability and radiation performances of SiC gate oxides are not widely known because SiC MOSFET devices are still at an RD level or in a pre-industrialisation phase for industrial applications. As a result, this study will have the goal of characterising SiC gate oxides as it is the key performance parameter in the future development of radiation-hardened SiC MOSFET devices. This proposed activity is considered a key stepping stone toward the development of radiation-hard high-voltage (600 Volt and greater) SiC power MOSFETs.This TRP activity can be divided into the following 4 tasks, namely:Task1: Prototyping a SiC MOS capacitor structure with different gate oxide processes, different stacks and different gate oxide layer thicknesses. The prototype devices will be assembled in hermetic packages in order to allow the high temperature and radiation testing which shall be conducted under Task 2.Task2: I-V and C-V characterisation before and after gate stress over temperature will be performed (the reliability test methodology needs to be agreed: e.g. time dependent dielectric breakdown ). The structure will then be submitted to constructional analysis to investigate the oxide/substrate interface quality after voltage/temperature stressTask3: The prototype devices will be characterised under TID testing, with different biasing, dose rate and annealing temperature conditions.Task4: SEGR performances vs. irradiation parameters (such as ion species, stopping power, range, flow) will be examined again using the above test vehicles, prototyped and packaged in Task 1. In all cases an evaluation based on Titus model will be performed in order to assess its possible validity in the case of SiC substrates.

• Application domain: Generic Technologies

•

Technology Domain:

23 - Electrical, Electronic and Electro-mechanical (EEE) Components and Quality

23 - Electrical, Electronic and Electro-mechanical (EEE) Components and Quality

•

Competence Domain:

1-EEE Components, Photonics, MEMS

1-EEE Components, Photonics, MEMS

• Initial TRL: TRL 4

• Target TRL: TRL 5

• Achieved TRL: TRL 5

•HarmoRoadMap: Power Management and Distribution (2008.2)

•IPC Document: ESA/IPC(2013)3,add.5