Very High Rate Turbo Decoder with interleaver in the TTCP

Programme Reference

T212-005GS

Status

Closed

Country

Portugal

Start Date

2020

End Date

2023

Programme: TDE Prime Contractor: DEIMOS ENGENHARIA S.A.

Subcontractors:

POLITECNICO DI TORINO • Italy

Objectives

Explore the different options and select the most efficient one to implement a very high data rate Turbo decoder and test encoder for Turbo rates 1/2, 1/4 and 1/6 working up to 80 Mbps in the TTCP, including the new CCSDS interleaver .Breadboard the selected option in an economic platform and demonstrate its scalability up to the required 80 Mbps in the TTCP.

Description

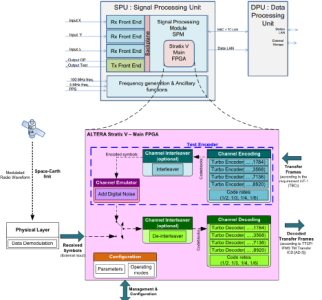

The Envision CDF exercise has concluded that a bit rate of 75 Mbps is required to comply with the data return strategy, mainly due to big quantity of data produced by the proposed SAR instrument.At the Venus distances the received power on earth is quite limited, requiring a very efficient modulation and coding system.Turbo rate 1/4 is a very efficient coding mode, allowing to go down to Eb/No of 0 to 0.25 dB, which is around 1 dB better than the LDPC 1/2 codes, which is the current solution used in EUCLID at these high data rates. However the current implementation of the Turbo rate 1/4 decoder in ESA ground stations TTCP only reaches 3 Mbps. Also Turbo rates 1/2 and 1/6 only reach 3 Mbps at present.Moreover Turbo codes do not perform well in a bursty channel, as can be the case of Solar conjunctions, due to the scintillation effects. The incorporation of the channel interleaver recommended in CCSDS would improve substantially the behaviour of Turbo codes (see presentation SLS-CS_17-13_V2 from K. Andrews- CCSDS-The Hague. Nov. 2017. AI_17_03)In order to achieve the required 80 Mbps, a new architecture for the on ground Turbo decoder in the TTCP has to be studied and designed, together with the interleaver. A parallelisation of the decoder is possible, and would allow reaching the required rates, but to fit it in the TTCP available resources is a difficult task that requires optimisation. The optimisation of the TTCP Turbo rate 1/4 (and rates 1/2 and 1/6) to reach 80 Mbps and the inclusion of the new interleaver are the goals of this activity.The development of the Turbo encoders for rate 1/2, 1/4 and 1/6 to support testing and validation is also part of the tasks of this activity.This activity is coordinated with TEC in the development of the on-board counterpart (STAT-4578). The activity will be divided in 4 tasks:1- Explore the different options and select the most efficient one to implement a very high data rate Turbo decoder and test encoder for Turbo rates 1/2, 1/4 and 1/6, working up to 80 Mbps in the TTCP. Study the interleaver recommended in CCSDS.2-Design the breadboard of the selected option in an economic platform and demonstrate its scalability up to the required 80 Mbps in the TTCP.3- Develop and test the breadboard.4- Produce the Test reports and Final report.

• Application domain: Space Science

•

Technology Domain:

12 - Ground Station Systems and Networks

12 - Ground Station Systems and Networks

•

Competence Domain:

8-Ground Systems and Mission Operations

8-Ground Systems and Mission Operations

• Initial TRL: TRL 3

• Target TRL: TRL 5

• Achieved TRL: TRL N/A

•HarmoRoadMap: Ground Station Technology (2015.2)

•IPC Document: N/A

•Public Document: