Verification of SEU-mitigation techniques in 3rd/4th generation Flash FPGAs

Programme Reference

T701-503ED

Status

Closed

Country

Spain

Start Date

2018

End Date

2020

Programme: TDE Prime Contractor: ARQUIMEA INGENIERIA SLU

Objectives

The objectives of this activity is the radiation characterization of the 4th generation of Flash FPGAs offered by Microsemi, and the development of methods for verifying the proper implementation of Single Event Upset/Transient (SEU/SET) mitigation techniques applied at Register Transfer Level (RTL) for 3rd and 4th generation Flash FPGA technologies.

Description

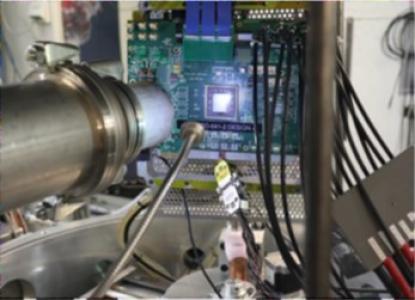

Flash FPGAs combine the reprogrammability and flexibility of SRAM-based FPGAS, with immunity to configuration upsets, low static power and a non-volatile configuration, which are characteristics more common to antifuse-based FPGAs. The latest developments in Flash-based FPGAs, e.g. the 4th generation Microsemi Flash FPGAs (RTG4), offer a high number of high-performance programmable logic resources, large and fast on-board memories, and high performance I/O - SERDES, LVDS, DDR, etc. All the elements are very appealing in high-bandwidth data processing payload applications, but also high performance on-board computing, if these FPGA resources are combined with on-chip processors. Targeting 3rd generation (ProASIC3) and 4th generation (RTG4) Flash-based FPGA technologies, this activity includes the following tasks: 1. Development of (formal) verification methods for verifying the proper implementation of SEU/SET mitigation techniques applied at RTL level (e.g. TMR, 'safe' Finite State Machines, etc). Formal methods are indicated as a suitable solution for this problem as they present several advantages compared to stimulus-based simulation methods: the fact that they don't require stimulus vectors in order to verify the equivalence of a mitigated design vs the original simplifies and shortens the verification task. Even more importantly, formal methods cover the complete design space exhaustively, hence their final proofs are more conclusive compared to simulation-based methods. 2. Preliminary radiation test campaign, targeting 4th generation Flash FPGAs, with the following aims: (a) Characterization of radiation-induced single event upsets (SEU) in I/O elements of the FPGA, and the effects of possible error mitigation techniques, such as TMR. ? Characterization of radiation-induced errors on-chip RAM blocks: analysis of occurrence, and possible patterns, of single and multiple bit upsets in on-chip RAMs. (b) Characterization of PLL performance degradation (sensitivity) under radiation. It is preferred that The test vehicles used as Designs Under Test (DUTs) in this activity are be selected considering the intended use of these FPGAs in On-Board Computers (OBC) and data handling applications, and could include on-board interfaces such as SpaceWire/SpaceFibre and CAN, to other representative designs used in DH applications, that could facilitate the proposed tests.

• Application domain: Generic Technologies

•

Technology Domain:

1 - On-board Data Subsystems

1 - On-board Data Subsystems

•

Competence Domain:

1-EEE Components, Photonics, MEMS

1-EEE Components, Photonics, MEMS

• Initial TRL: TRL 2

• Target TRL: TRL 4

• Achieved TRL: TRL 4

•HarmoRoadMap: Data Systems and On Board Computers (2011.2)

•IPC Document: ESA/IPC(2016)3||ESA/IPC(2016)3,add.3

•Public Document: